正品保证

所有产品原厂质量保证

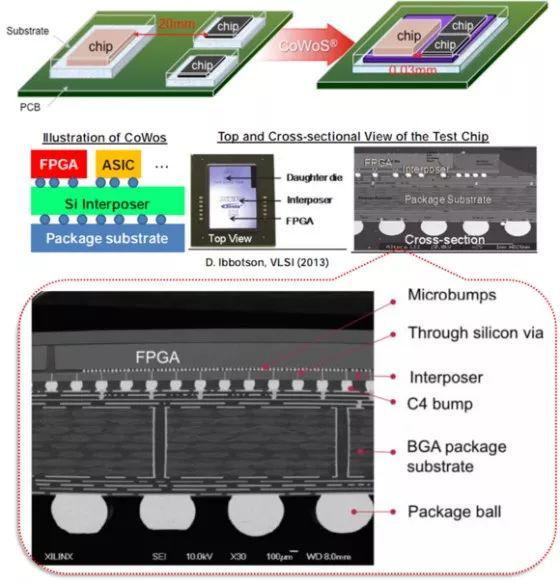

CoWoS是指衬底上晶圆级芯片封装,是英文Chip on Wafer on Substrate的缩写,属于一种集成型先进半导体封装技术。其缺点是成本太过高昂,只有苹果、赛灵思(Xilinx)、台积电等少数一线厂商采用。

CoWoS是指衬底上晶圆级芯片封装,是英文Chip on Wafer on Substrate的缩写,属于一种集成型先进半导体封装技术。其缺点是成本太过高昂,只有苹果、赛灵思(Xilinx)、台积电等少数一线厂商采用。

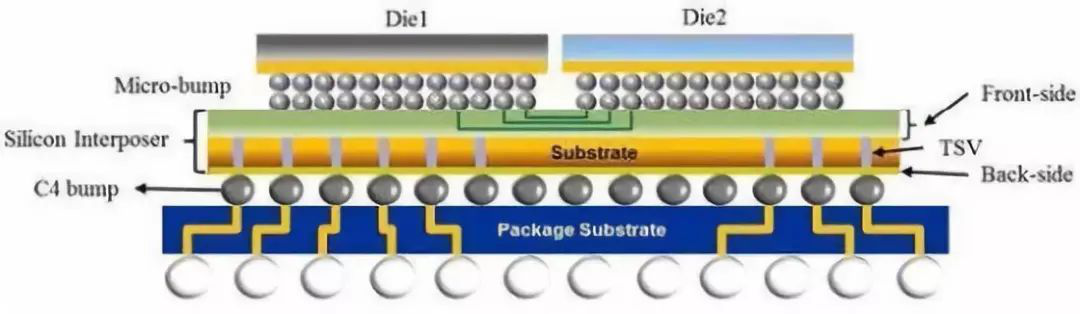

CoWoS是晶圆段延伸的先进封装技术,先将半导体芯片通过Chip on Wafer(CoW)的封装制程连接至矽晶圆,再把此CoW芯片与基板连结,集成而成CoW-on-Substrate。

2017年,Google在AlphaGo中使用的TPU 2.0也采用CoWoS封装。

2017年,英特尔的Nervana也不例外的交由台积电代工,采用CoWoS封装。

由于产能供不应求,台积电首度扩充CoWoS半导体封测产能。

目前,第三代CoWoS封装技术能够提供现行约26x32mm倍缩光罩;而将于2019年量产的第四代CoWoS能提供现行2倍倍缩光罩,约1700平方毫米;而将于2020年量产的第五代CoWoS能提供现行3倍倍缩光罩,约2500平方毫米。

由于倍缩光罩尺寸越大,可搭载更多不同的芯片、提供更大的核心面积、有更多的接脚数,让芯片功能更多元化、提升算力,最新、最高阶的芯片都必须用CoWoS半导体封装技术,这可以让产品的效能提升3-6倍。目前,CoWoS已经获得NVIDIA、AMD、Google、XilinX、华为海思等高端芯片厂商的订单。